EP2C5T144 Development Board Tutorial

#fpga

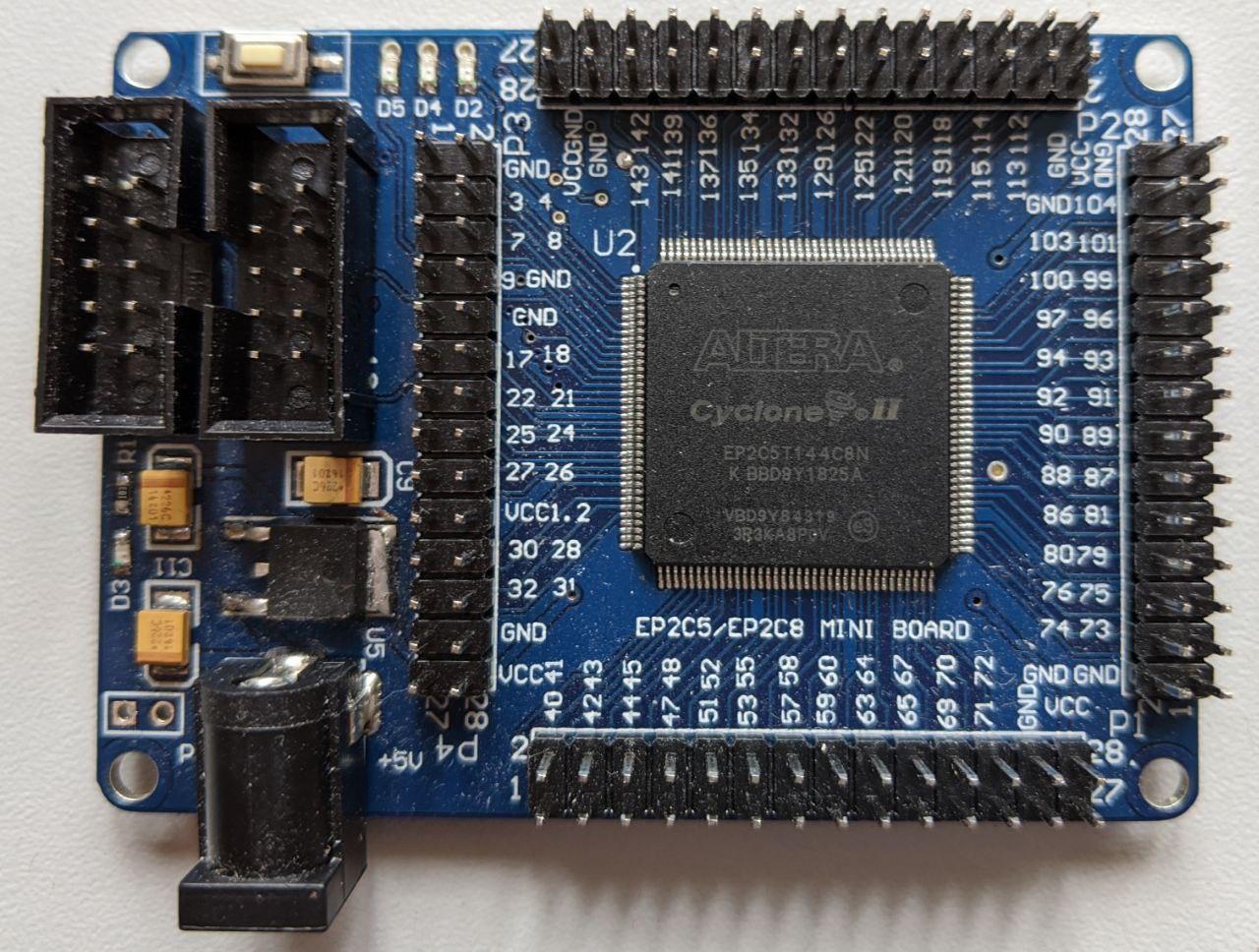

Das EP2C5T144 Development Board ist für unter 20€ unter anderem bei eBay und Amazon erhältlich. Leider ist der Einstieg in die Programmierung dieses Boards mit VHDL nicht ganz einfach. Diese Seite listet Ressourcen auf, die mir beim Einstieg geholfen haben.

- land-boards.com: Wiki mit ein paar allgemeinen Daten.

- youtube.com: Einstiegsvideo in die Programmierung. Achtung: Enthält Fehler. Es ist hilfreich die Kommentare zu lesen!

- openimpulse.com, leonheller.com: Download des Schaltplans

Inhaltsverzeichnis

Schaltplan und Pins

Eigentlich ist der Schaltplan recht selbsterklärend. Fast alle Pins sind auf die vier langen Pinheader rausgeführt. Allerdings gibt es folgende Besonderheiten:

Besondere Pins

PIN144ist über den Taster mitGNDverbunden (falls der Taster benutzt werden soll, muss ein Pull-Up-Widerstand einprogrammiert werden).PIN17ist mit dem50MHz-Oszillator verbunden.PIN3,PIN7,PIN9sind jeweils über eine LED mitVCC3.3verbunden.

Nicht nutzbare Pins

PIN26ist überR1(0Ω) fest mitVCC1.2verbunden.PIN27ist überR2(0Ω) fest mitGNDverbunden.PIN80ist überR9(0Ω) fest mitGNDverbunden.PIN81ist überR10(0Ω) fest mitVCC1.2verbunden.PIN73ist überR13(10kΩ) mitVCC3.3und überC14(10µF) mitGNDverbunden.

Diese Pins können daher nicht als I/O Pins benutzt werden. Man kann die 0Ω-Widerstände mit etwas Geschick aber entfernen. Laut land-boards.com sind diese Pins so komisch angeschlossen, um auch mit einem anderen FPGA, dem EPC28, kompatibel zu sein.

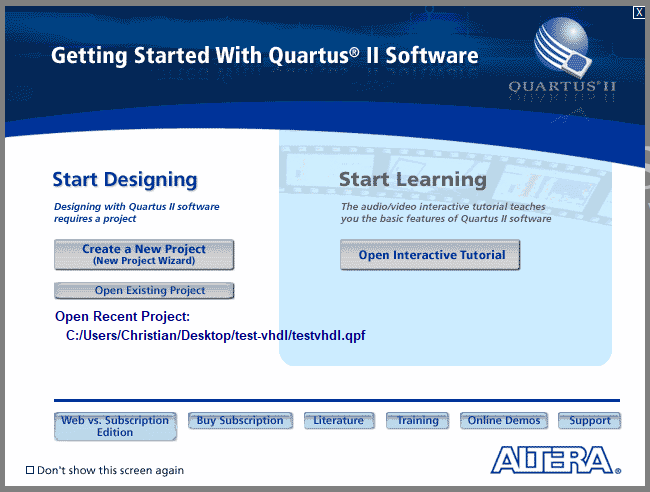

Programmierung

Die Programmierung erfolgt mit der kostenlosen Quartus II Software. Allerdings unterstützten aktuelle Versionen den genutzten FPGA nicht mehr. Die letzte Version, die den FPGA unterstützut, ist Quartus 13.0SP1. Die Software kann hier heruntergeladen werden: https://fpgasoftware.intel.com/13.0sp1/?edition=subscription&platform=windows

Setup

- Klick auf “Create a New Project”

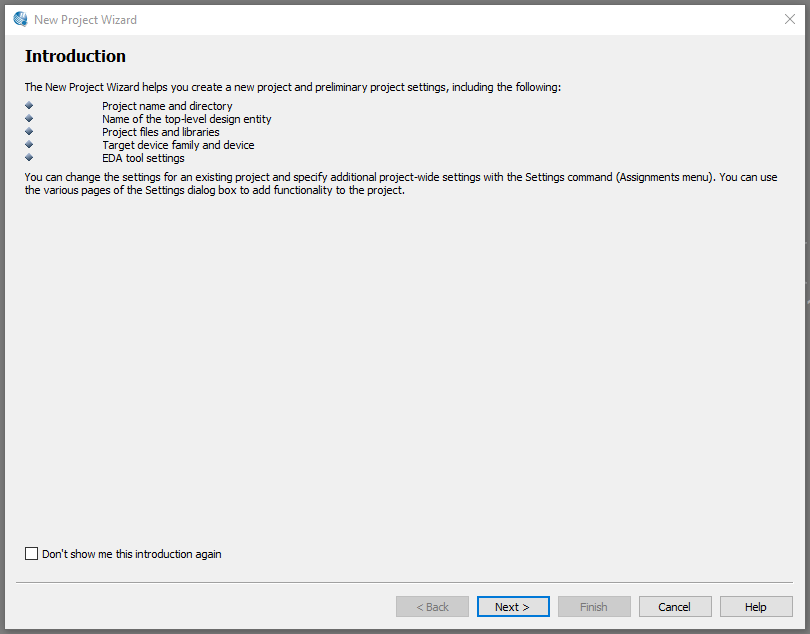

- Klick auf “Next”

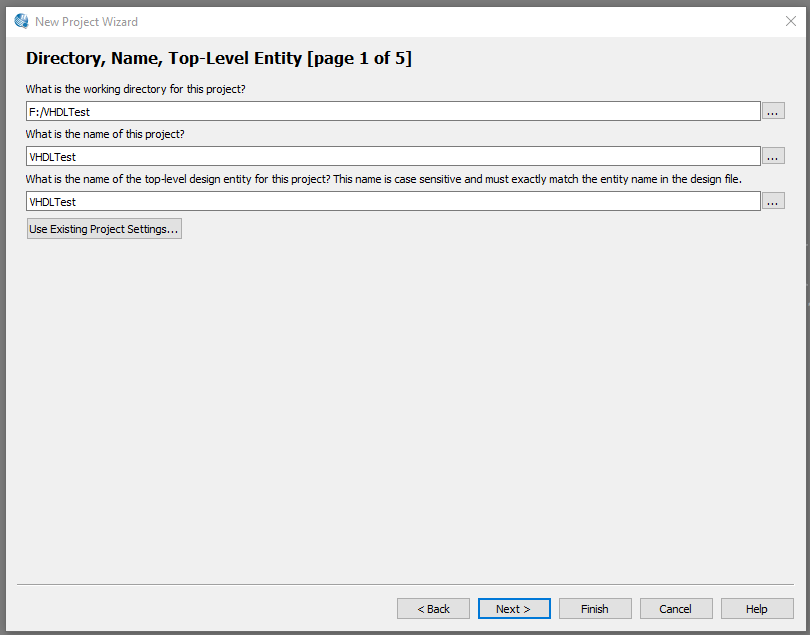

- Namen und Speicherort für das Projekt vergeben, danach Klick auf “Next”

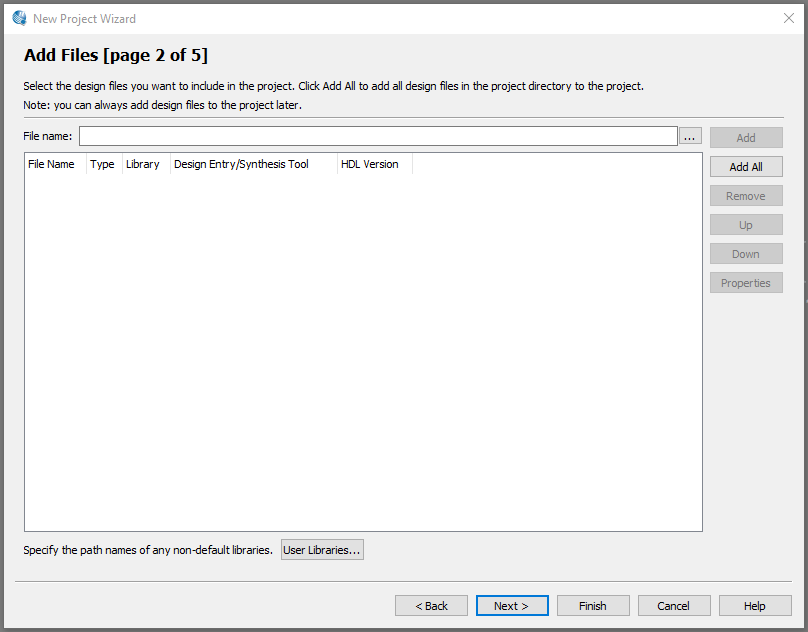

- Klick auf “Next”

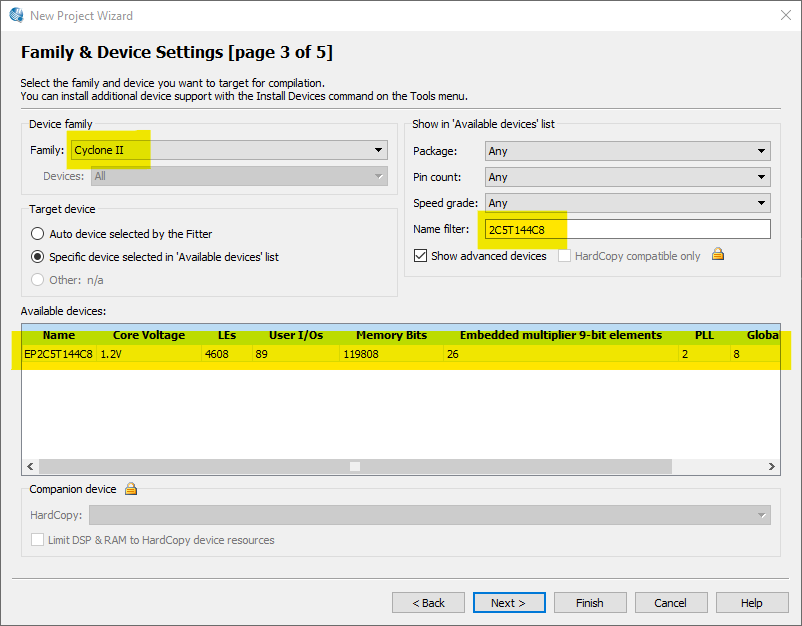

- FPGA auswählen, danach Klick auf “Next”

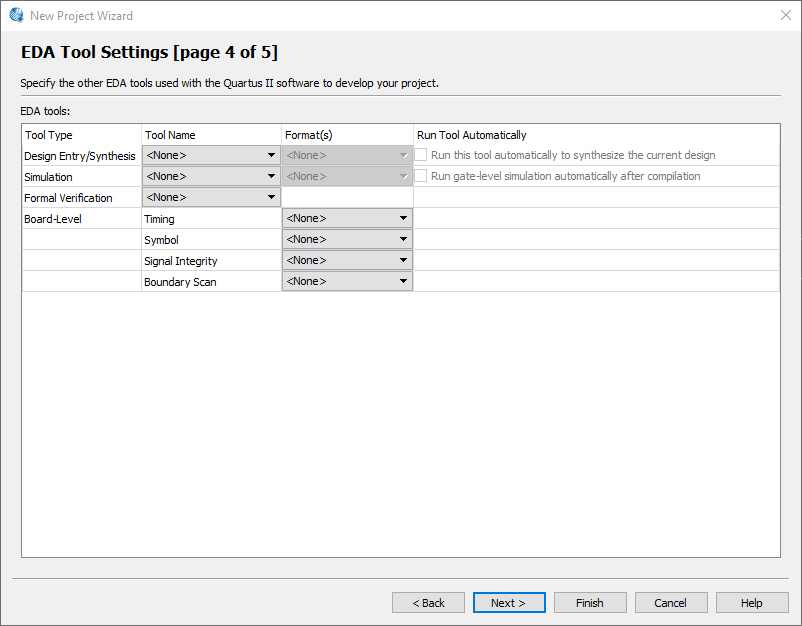

- Klick auf “Next”

- Klick auf “Next”

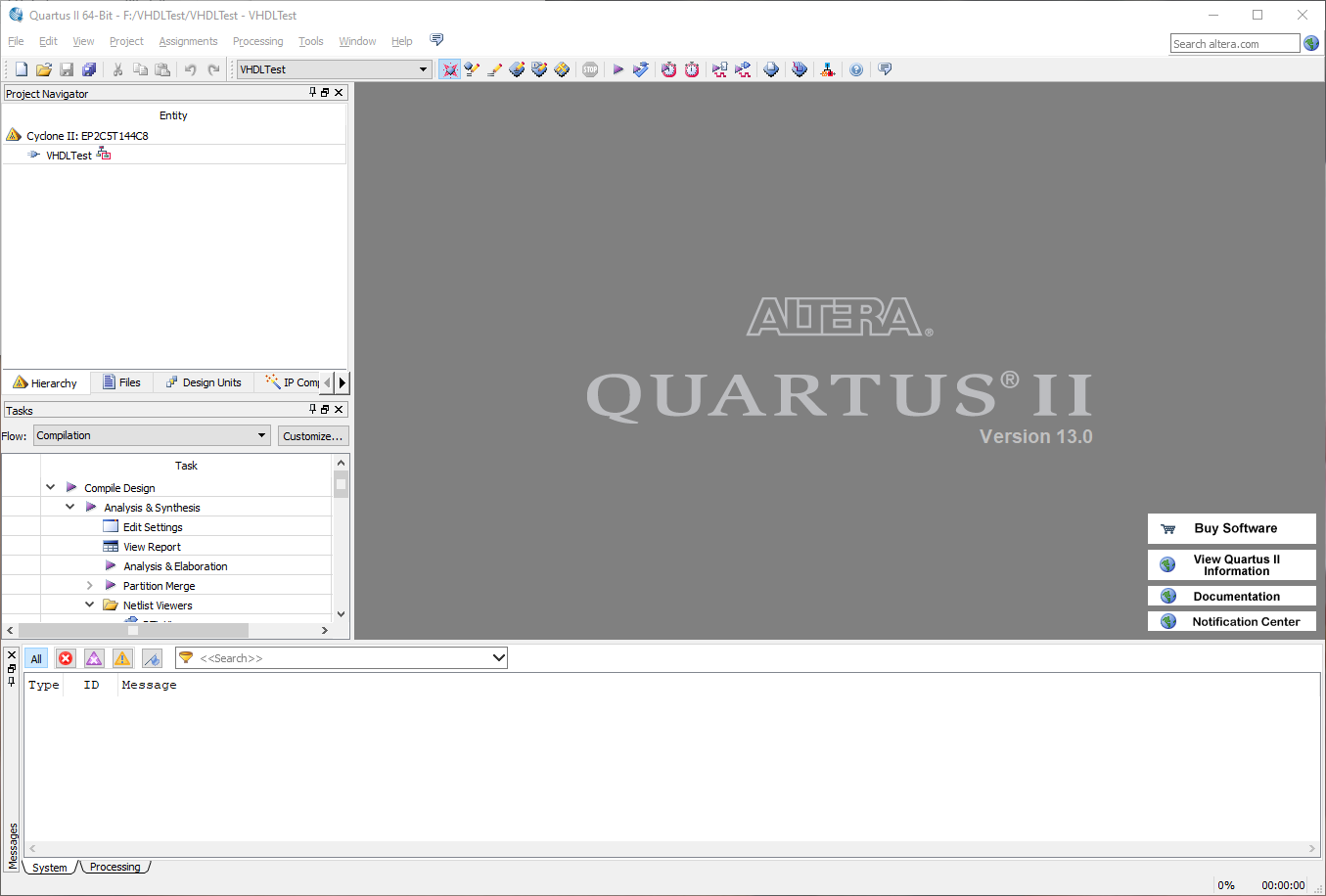

- Das erstellte Projekt wird geöffnet.

Als nächstes sollte noch eine wichtige Option geändert werden.

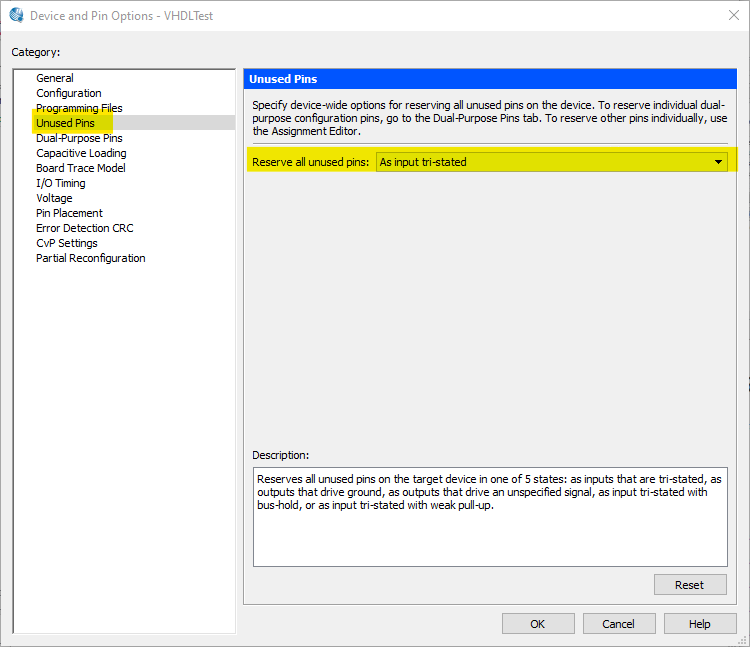

Standardmäßig werden alle nicht benutzten Pins nämlich mit GND verbunden.

Das führt aber zu einem Kurzschluss, da wie oben beschrieben einige Pins ja mit VCC verbunden sind.

Daher sollte man in den “Device”-Einstellungen einstellen, dass alle unbenutzten Pins als “input tri-stated” programmiert werden:

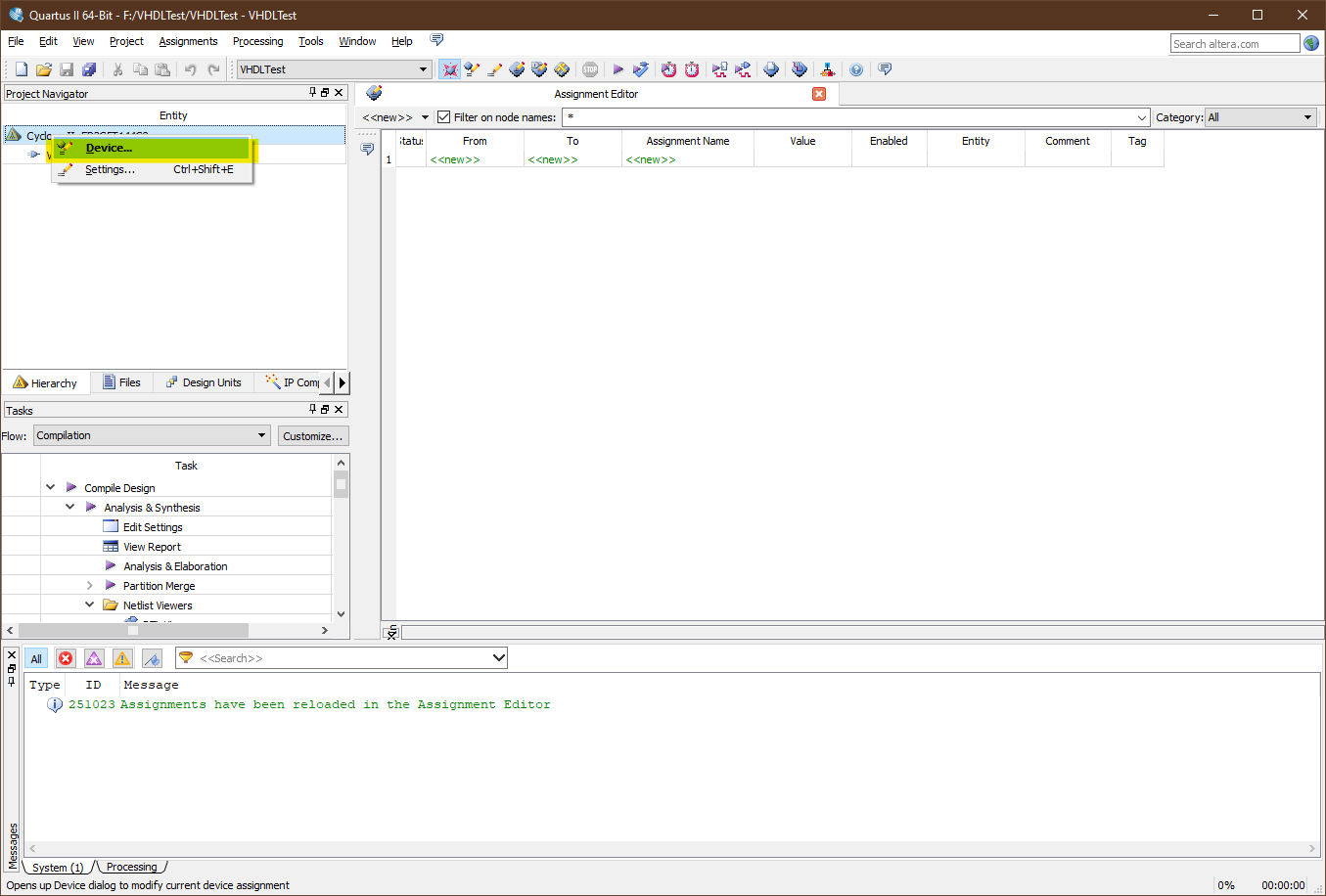

- Rechtsklick auf das Projekt, dann auf “Device…”

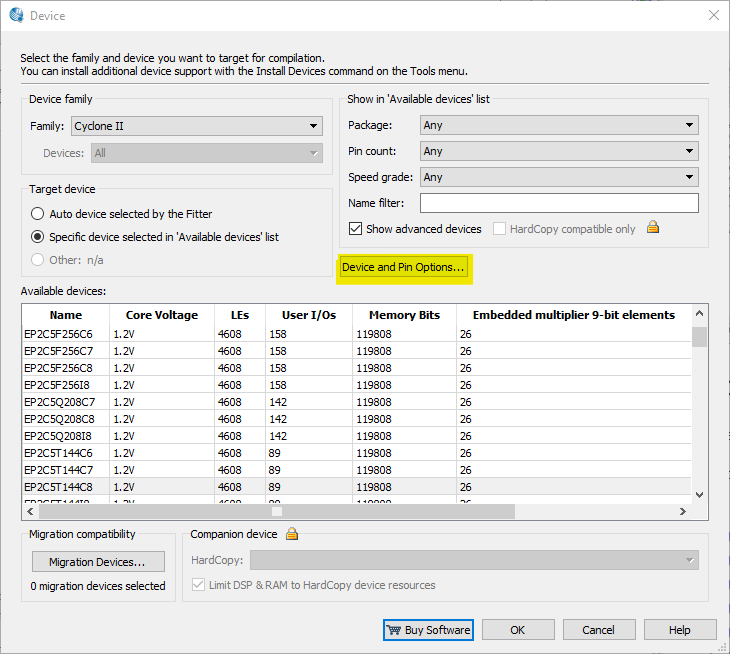

- Klick auf “Device and Pin Options…”

- Klick auf “Unused Pins” und dann Auswahl von “As input tri-stated”

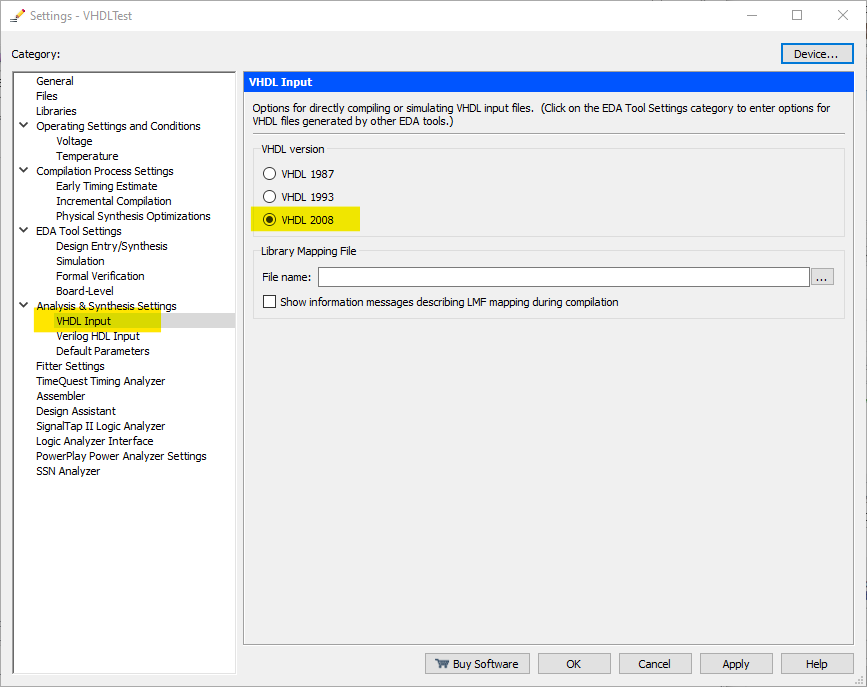

Desweiteren kann man in den Einstellungen noch den VHDL-Standard auf “VHDL 2008” stellen, um modernere VHDL-Features nutzen zu können:

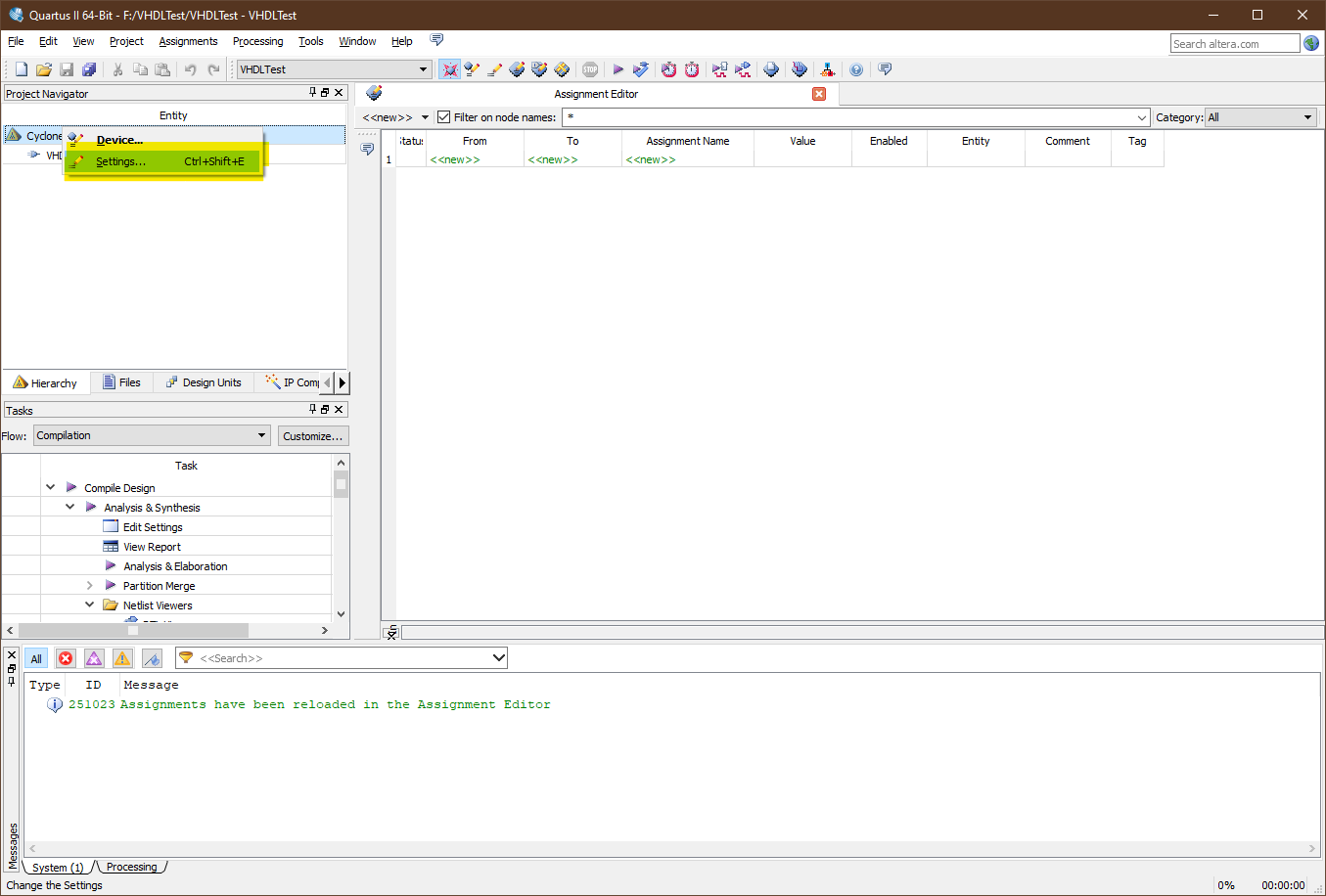

- Rechtsklick auf das Projekt, dann auf “Properties…”

- Auswahl von “VHDL 2008”

Top-Level Entity Erstellung und Pin Planner

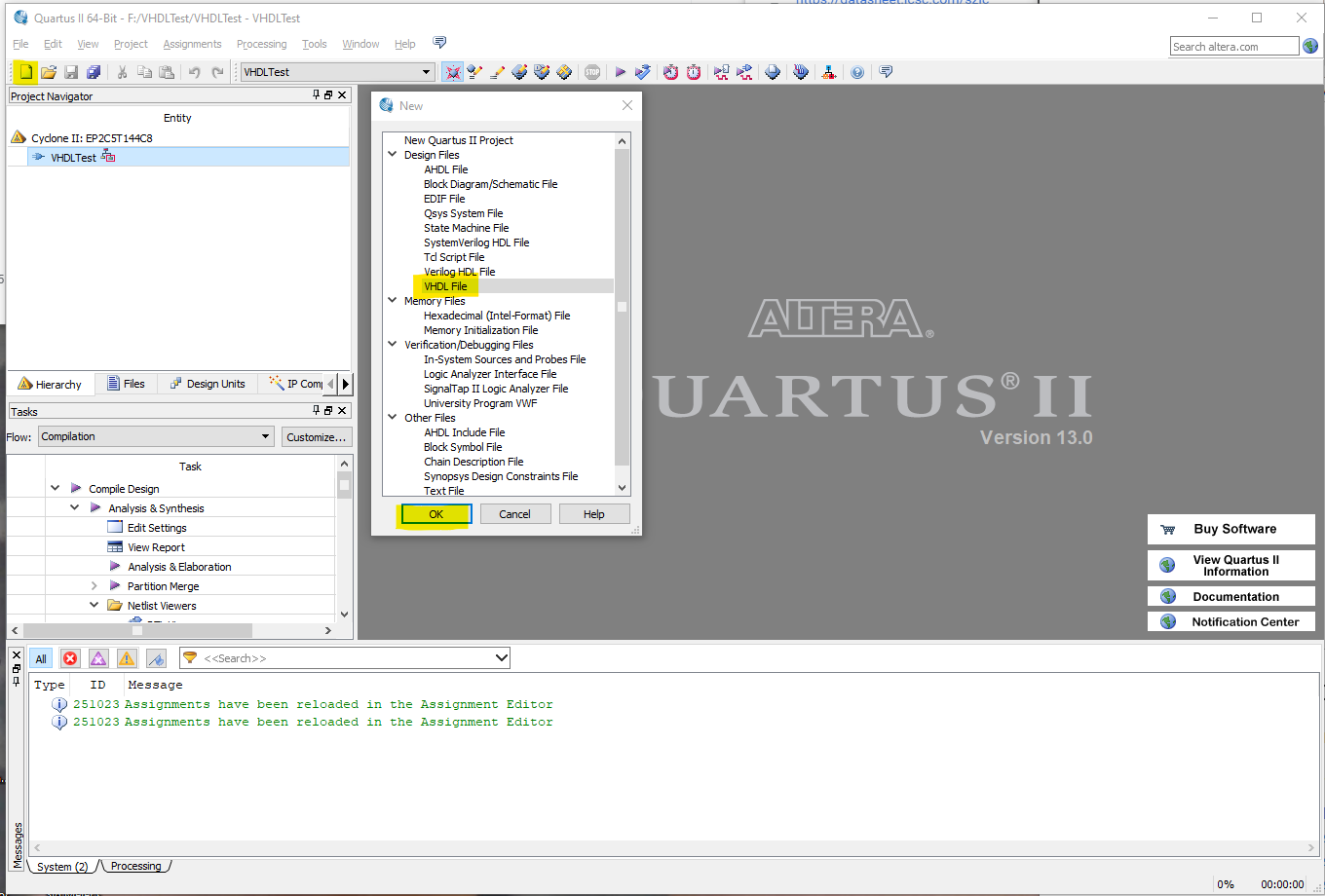

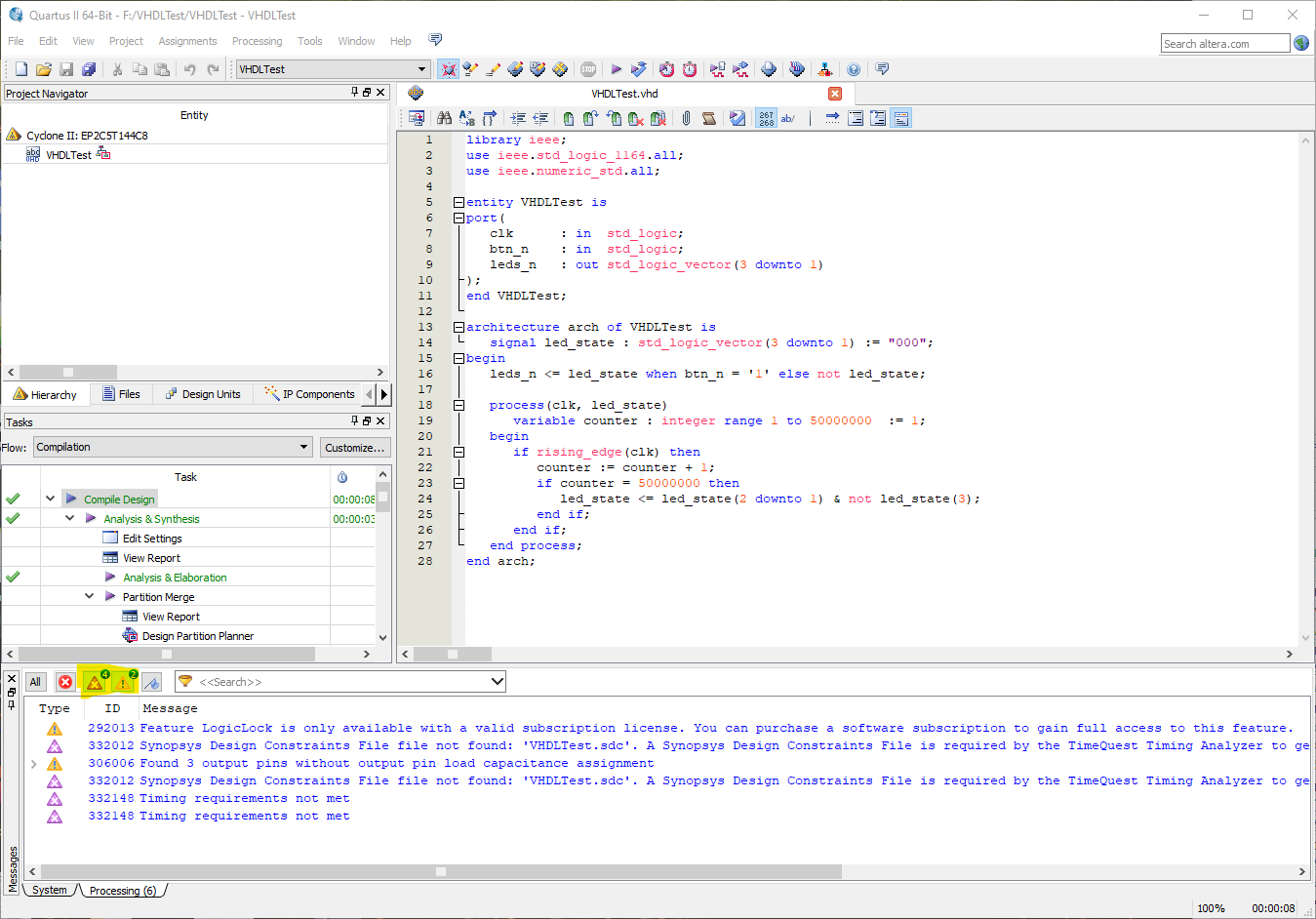

- Wir erstellen nun eine Top-Level Entity, die den gleichen Namen wie das Projekt hat:

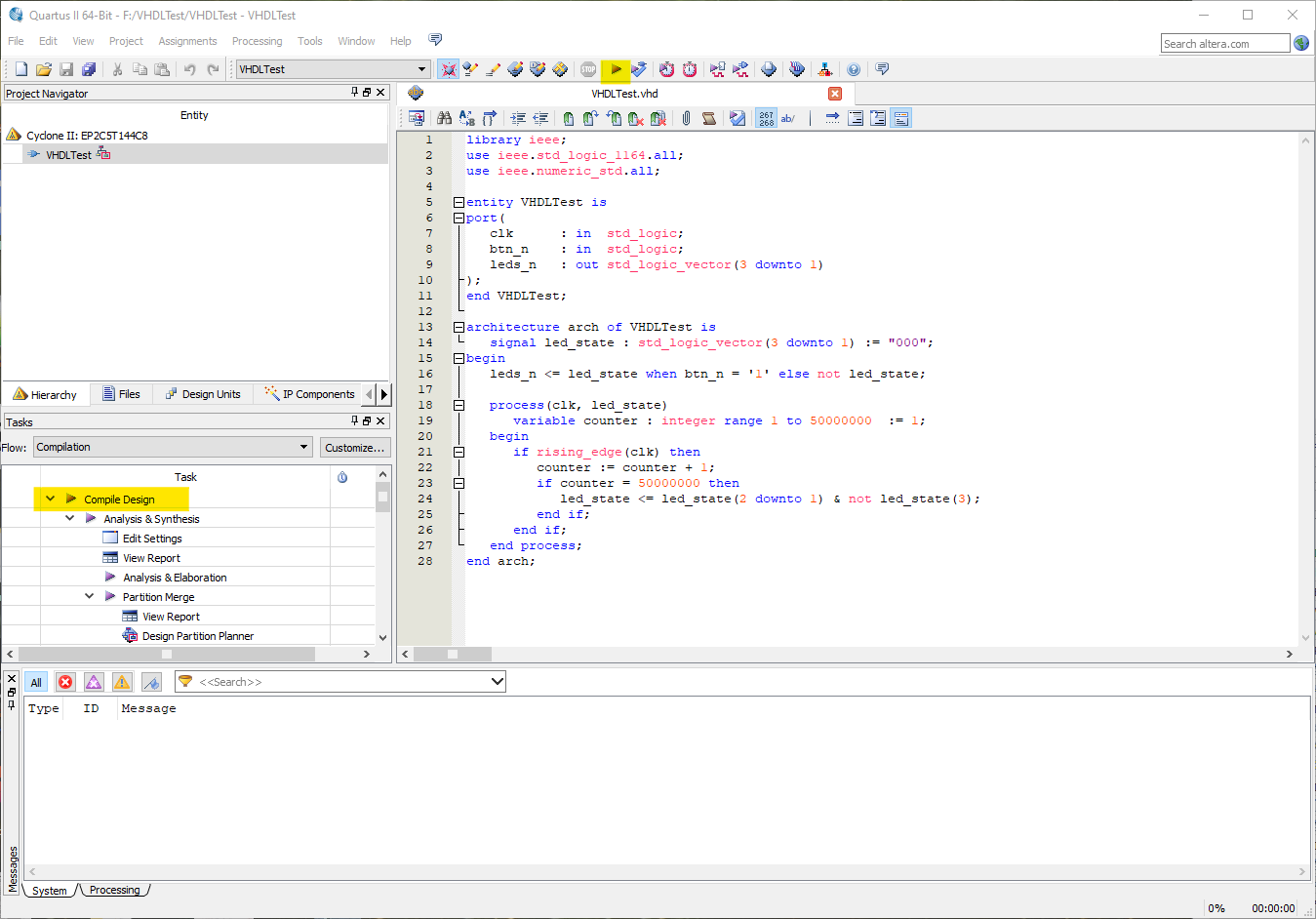

- Zum Testen lassen wir die LEDs mittels eines Möbiuszählers blinken.

Während der Knopf gedrückt wird, invertieren wir die Signale.

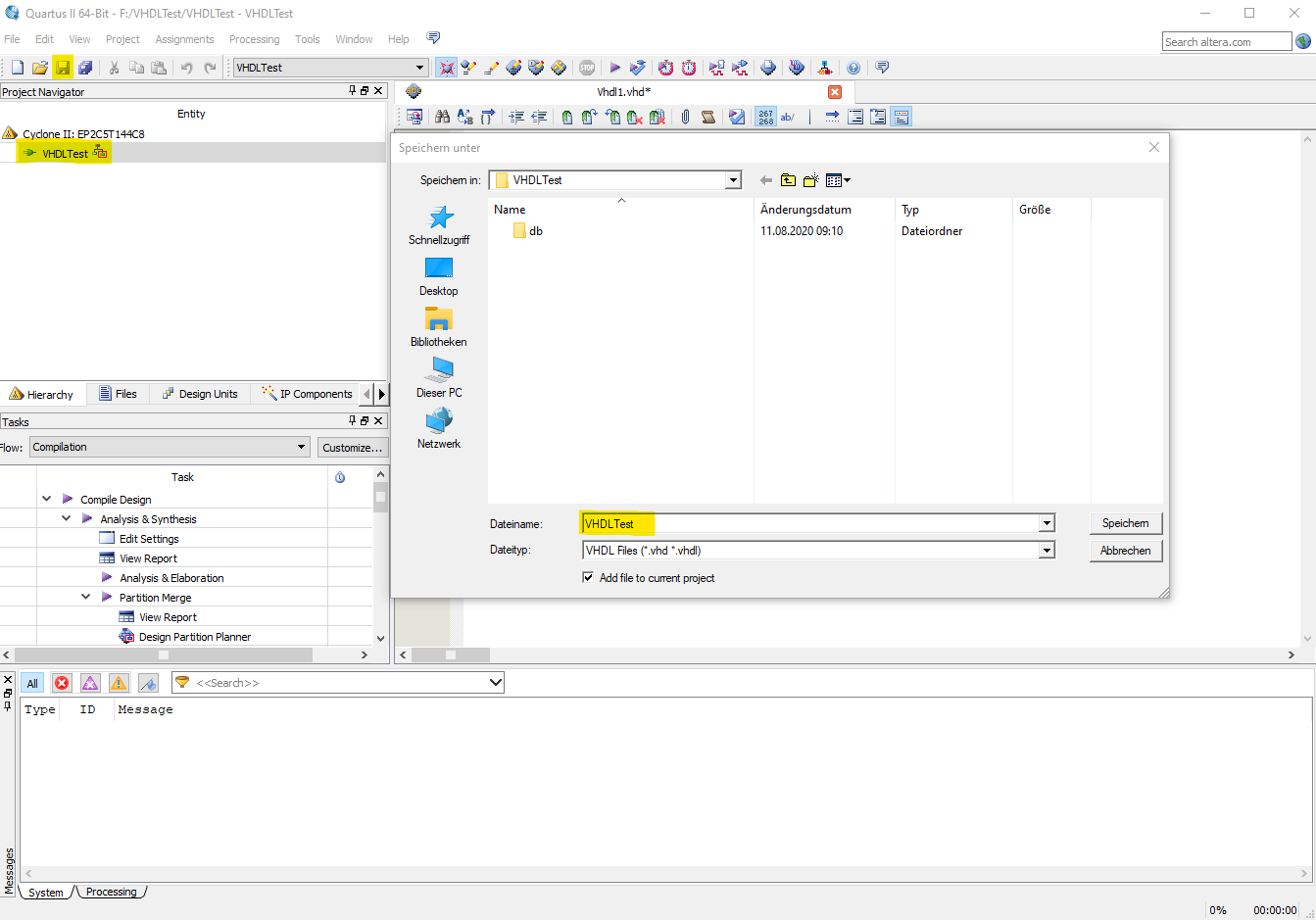

library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; entity VHDLTest is port( clk : in std_logic; btn_n : in std_logic; -- Per Konvention fügen wir an alle Signale mit negativer Logik ein _n suffix an. leds_n : out std_logic_vector(3 downto 1) ); end VHDLTest; architecture arch of VHDLTest is signal led_state : std_logic_vector(3 downto 1) := "000"; begin leds_n <= led_state when btn_n = '1' else not led_state; process(clk, led_state) variable counter : integer range 1 to 50000000 := 1; begin if rising_edge(clk) then counter := counter + 1; if counter = 50000000 then led_state <= led_state(2 downto 1) & not led_state(3); end if; end if; end process; end arch; - Wir speichern die neue Datei mit dem gleichen Namen wie das Projekt.

- Nun können wir das Design testweise kompilieren:

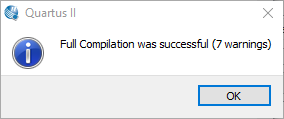

- Das sollte klappen und mit folgender Meldung bestätigt werden:

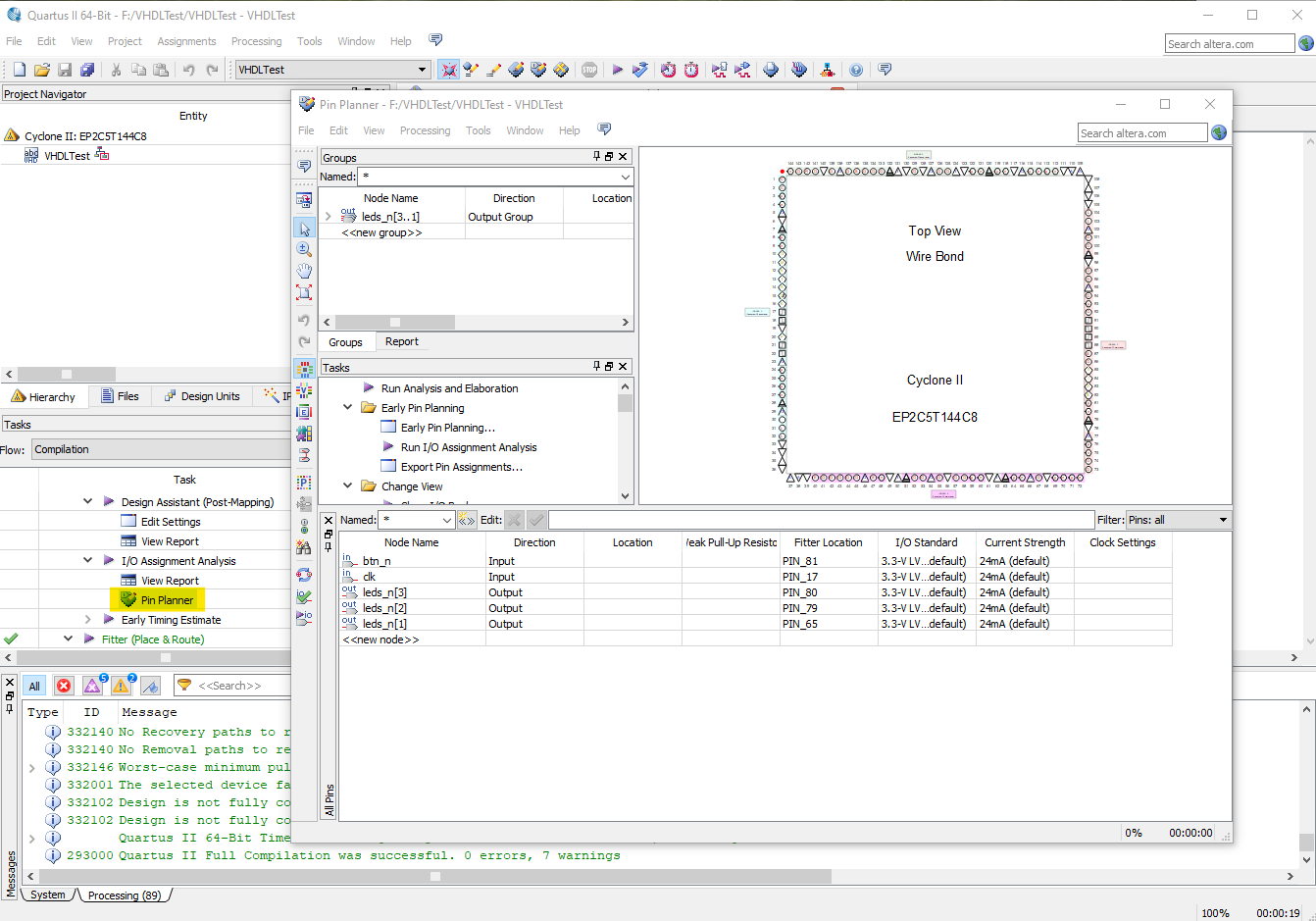

- Bevor wir das Design auf das Board übertragen können, müssen wir noch alle Ein- und Ausgangssignale der Top-Level Entity den entsprechenden Pins zu weisen. Dazu öffnen wir den Pin Planner:

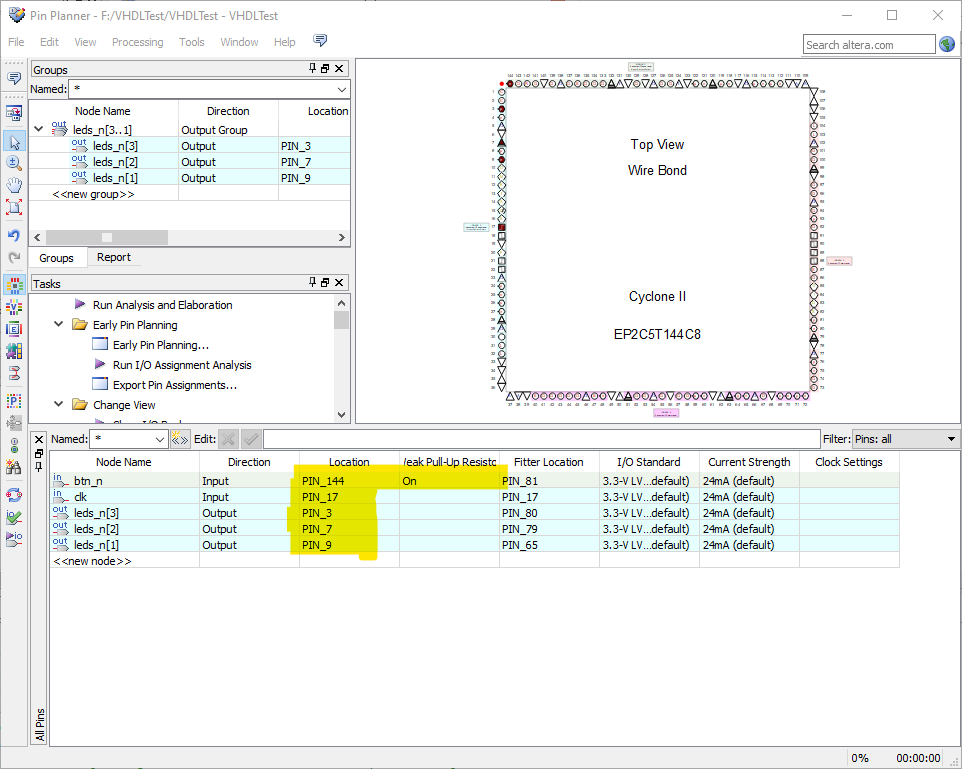

- Für uns sind nur die beiden Spalten “Location” und “Weak Pull-Up Resistor” relevant. Hier werden den Signalen die physischen Pins zugeordnet. Wir wählen die Pins natürlich so, wie sie auf unserem Board belegt sind. Danach schließen wir den Pin Planner wieder:

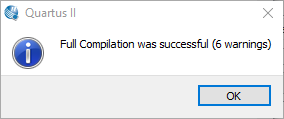

- Nun können wir nochmal kompilieren und sollten eine Warnung weniger erhalten. Die verbleibenden Warnungen können wir getrost ignorieren:

Programmieren über JTAG

Die Programmierung über JTAG ist nicht persistent, d.h. nach dem nächsten aus- und anschalten des Board läuft wieder das im EEPROM auf dem Board gespeicherte Programm.

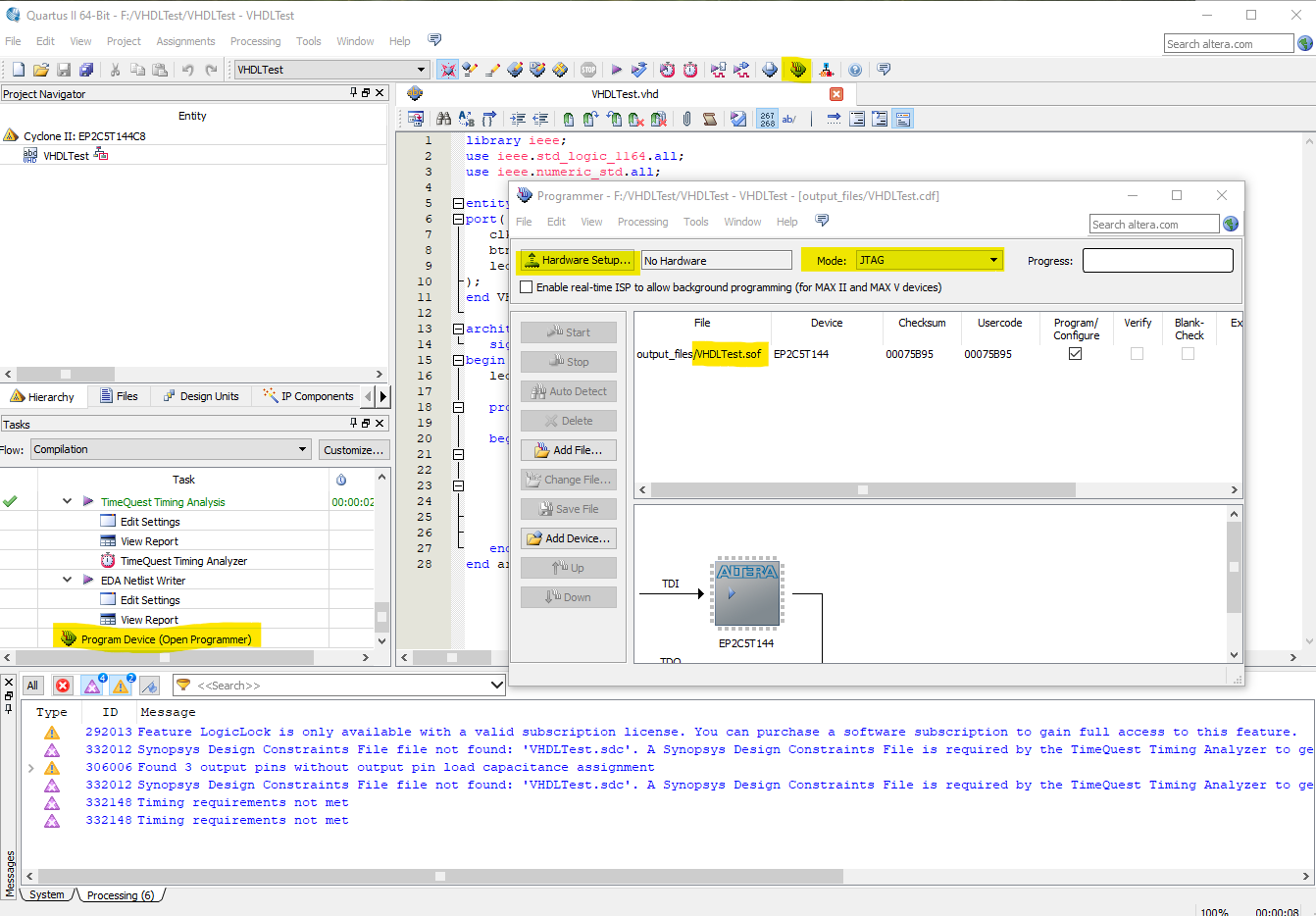

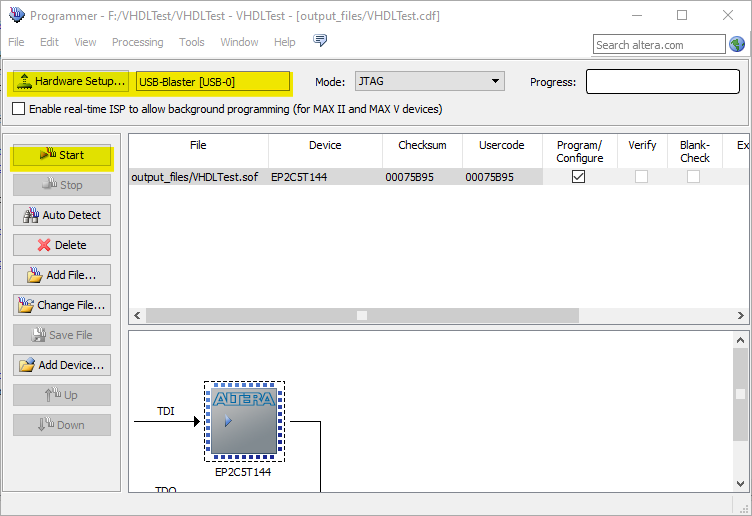

- Um das Design auf das Board zu übertragen, schließen wir den USB-Blaster an den Computer an und verbinden ihn mit dem rechten “JTAG” Sockel auf dem Board. Danach öffnen wir den Programmer.

Dort stellen wir sicher, dass “JTAG” ausgewählt ist und klicken danach auf “Hardware Setup”:

- Hier sollte der USB-Blaster auftauchen, den wir unter “Currently selected hardware” auswählen:

- Nun können wir das Design per Klick auf “Start” auf das Board übertragen:

Programmieren des EEPROM

Um ein Design dauerhaft auf dem FPGA zu speichern, müssen wir den EEPROM auf dem Board programmieren.

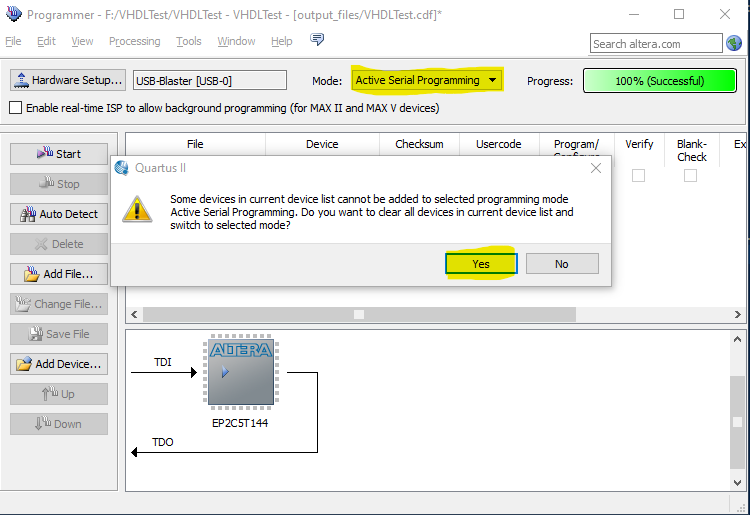

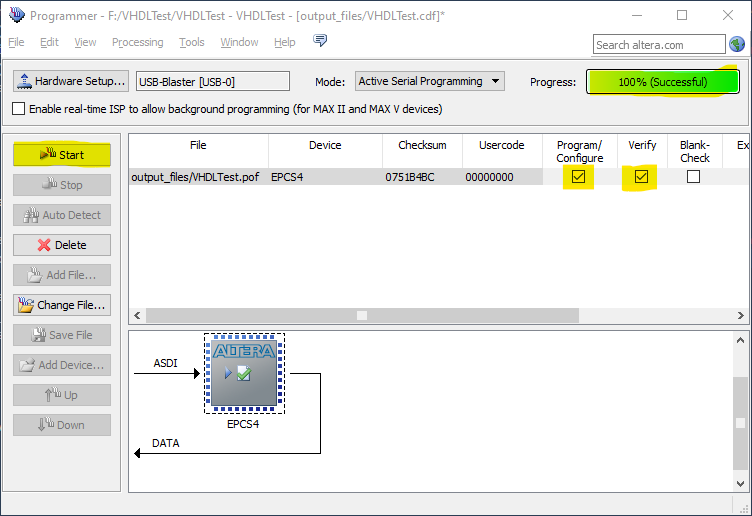

- Zuerst stellen wir den “Mode” von “JTAG” auf “Active Serial Programming”. Die ggf. erscheinende Warnung können wir ignorieren:

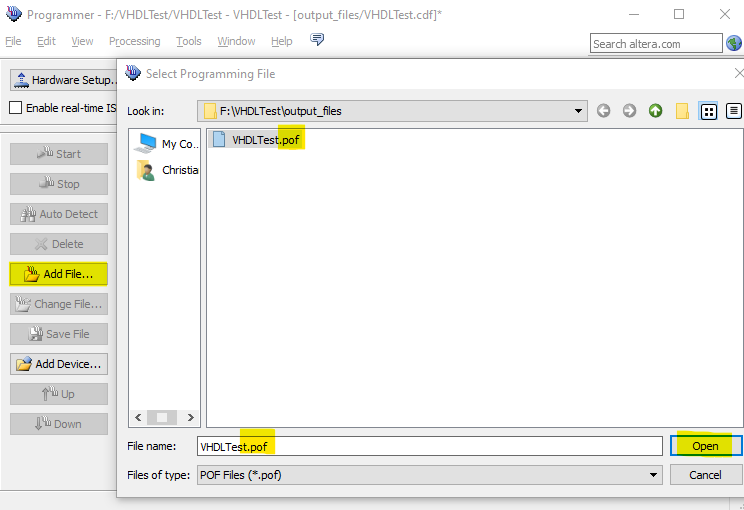

- Nun müssen wir über “Add File” die “VHDLTest.pof“-Datei auswählen:

- Schließlich wählen wir sowohl “Program/Configure” als auch “Verify” aus und klicken abschließend auf “Start”:

Achtung: Das Design wird erst gestartet, wenn man den USB-Blaster wieder in den JTAG-Port steckt oder ausstöpselt.

Downloads und weitere Dateien

Alle Dateien befinden sich in meinem GitHub Repository im Ordner EP2C5T144.

Enthaltene Dateien:

- board.jpg

- screenshots/1-project.png

- screenshots/10-device-options.png

- screenshots/11-unused-pins.png

- screenshots/12-settings.png

- screenshots/13-vhdl-version.png

- screenshots/14-new-file.png

- screenshots/16-new-file-save.png

- screenshots/17-compile.png

- screenshots/18-compile-success.png

- screenshots/19-pin-planner.png

- screenshots/2-introduction.png

- screenshots/20-pin-planner.png

- screenshots/21-success.png

- screenshots/22-warnings.png

- screenshots/23-programmer.png

- screenshots/24-hardware-setup.png

- screenshots/25-hardware-selection.png

- screenshots/26-program.png

- screenshots/27-program-eeprom.png

- screenshots/28-add-file.png

- screenshots/29-program.png

- screenshots/3-name.png

- screenshots/4-files.png

- screenshots/5-device.png

- screenshots/6-tool-settings.png

- screenshots/7-summary.png

- screenshots/8-done.png

- screenshots/9-device.png